Barcelona, 2-5 d’Octubre de 2017.- Investigadors del BSC han publicat els primers paràmetres de temps fiables i detallats de la memòria Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), permetent una simulació fiable a nivell de sistema d’aquesta tecnologia. Els paràmetres ha sigut avui presentats a la conferència titulada The International Symposium on Memory Systems 2017 (MEMSYS) que té lloc entre el 2 i el 5 d’octubre de 2017 a la ciutat de Washington DC. L’enfocament del BSC en la simulació de memòria STT-MRAM s’ha realitzat amb la cooperació d’Everspin Technologies Inc., líder mundial en el disseny i producció de STT-MRAM .

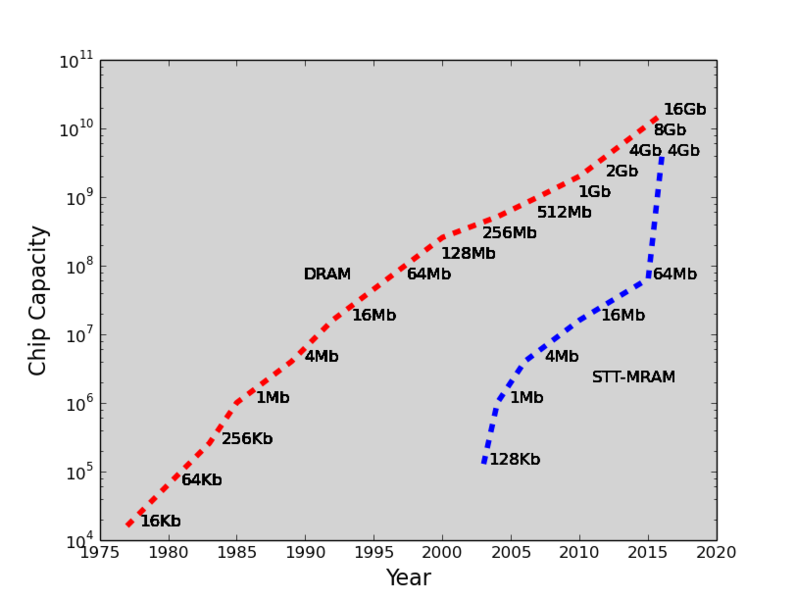

STT-MRAM és una tecnologia de memòria prometedora amb un conjunt de propietats molt atractives tals com la no-volatilitat, byte-addressability i una alta resistència. Té el potencial per convertir-se en la memòria universal que podria incorporar-se a tots els nivells jeràrquics de memòria. Com a memòria principal, STT-MRAM està atrapant ràpidament la tecnologia DRAM madura, tal i com es mostra a la figura 1; com a resultat, ha atret un notable interès per part d’un gran número dels principals fabricants de memòria. No obstant, la investigació acadèmica actual en STT-MRAM és marginal, degut principalment a que no s’han estandarditzat ni compartit per cap industria paràmetres de temps ben definits y fiables. D’aquesta manera, els investigadors segueixen tenint problemes per a realitzar una simulació de memòria STT-MRAM fiable.

“Un esforç intensificat en la investigació de STT-MRAM per part dels fabricants de memòria pot ser indicatiu que una revolució amb la tecnologia de memòria STT-MRAM és imminent, i esperem veure molts assoliments interessants en aquesta tecnologia en el futur pròxim. Ara que s’han publicat paràmetres de temps detallats i fiables, instem fortament a l’acadèmia que explori les oportunitats que aquesta tecnologia té per oferir” conclou Petar Radojkovic, líder de Memory Systems for HPC al BSC.

Amb l’objectiu de superar aquest problema, l’estudi del BSC analitza a fons i publica paràmetres de temps detallats sobre la memòria STT-MRAM per a facilitar una simulació fiable a nivell de sistema d’aquesta tecnologia. L’estudi es basa en el fet que els dispositius de memòria STT-MRAM estan i seran incorporats en el protocol i interfície de DDRx, indicant que la majoria de timings no canviaran de la memòria DRAM a STT-MRAM. En quan als paràmetres que sí que són diferents degut a les diferències entre les cèl·lules d’emmagatzematge DRAM i STT-MRAM, el millor que es pot fer és un anàlisis de sensibilitat d’aquests. L’estudi també suggereix rangs raonables per a aquests timings que es verifiquen amb productes comercialitzats.

Figura 2: Kazi Asifuzzaman (estudiant pre-doctoral al BSC) presentant a la MEMSYS Conference 2017.