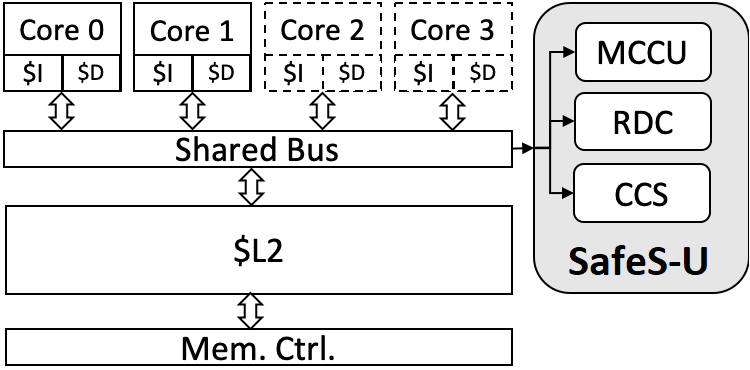

Researchers of the Barcelona Supercomputing Center (BSC) contributed to the first version of the De-RISC MPSoC platform and the Performance Monitoring Unit, integrating observability (Cycle Contention Stack, Request Duration Counter) and controllability capabilities (Maximum-Contention Control Unit). In particular, BSC experts have completed the implementation of the SafeS-U, a Performance Monitoring Unit to measure and control multicore time interference, thus easing the development and validation of safety-related real-time systems on the De-RISC platform.

“De-RISC builds upon the non-proprietary RISC-V Instruction Set Architecture (ISA) to remove export restrictions in the space domain, and incorporates time predictability and validation technology from BSC”, says Jaume Abella, principal investigator of the De-RISC project at BSC.

This is one of the major contributions of BSC developed in the first project year of the European project De-RISC whose aim was to pave a way to power future space and aeronautical applications with European technology. The project will guarantee access to made-in-Europe technology for aerospace applications through the use of RISC-V Instruction Set Architecture (ISA) in its final platform removing export restrictions from proprietary ISAs.

In the following months, the project’s consortium will continue demonstrating its commitment to the De-RISC technology and BSC researchers will focus on the performance validation of the platform.

For more information about De-RISC project and BSC developments within the project, please refer to De-RISC Publications (2020), ADA user journal vol41(2).

De-RISC press release: https://derisc-project.eu/de-risc-first-anniversary/

About De-RISC

De-RISC (Dependable Real-time Infrastructure for Safety-critical Computer) is a 30-month Innovation Action partially funded by the European Commission, which was launched in October 2019. With a budget of € 3,444,625, the project addresses computer systems within the space and aviation domains. It will introduce a market-ready hardware-software platform based on the RISC-V instruction set architecture (ISA), productizing a multi-core RISC-V system-on-chip designed by Cobham Gaisler and an efficient time and space partitioning based on the fentISS XtratuM hypervisor.

The project consortium comprises four partners, all of whom have extensive experience in the safety-critical and aerospace domains. The XtratuM hypervisor by fentISS (Spain) has been selected for different space missions including the OneWeb satellite constellation, the PLATINO generic satellite for constellations, and ARGOS-NEO ANGELS, EyeSat, SVOM, JUICE and MMX among others. The LEON processor series developed by Cobham Gaisler has been used in a variety of ESA missions. Barcelona Supercomputing Center is one of the leading research institutions in Europe and has closely collaborated with Gaisler and Thales in European projects such as SAFURE and PROXIMA. Thales is a world leader for mission critical information systems with ample experience in the aerospace, telecommunications and security domains.