- Status:

- Granted

- Publication number:

- US8561043

- Priority date:

- Inventor:

- Eduard Ayguade Parra, Tong Chen, Alexandre E Eichenberger, Marc Gonzalez Tallada, Xavier Martorell Bofill, John K O'Brien, Kathryn M O'Brien, Zehra N Sura, Tao Zhang

- Applicant:

- Barcelona Supercomputing Center - Centro Nacional De Supercomputacion (BSC-CNS), International Business Machines Corp (IBM)

Abstract

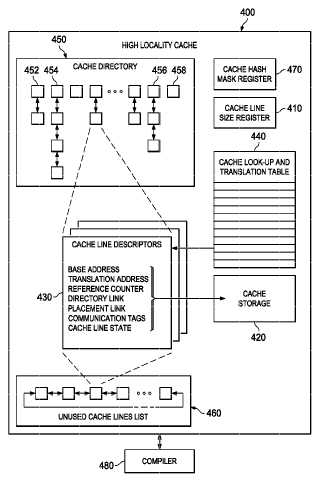

Mechanisms are provided for optimizing irregular memory references in computer code. These mechanisms may parse the computer code to identify memory references in the computer code. These mechanisms may further classify the memory references in the computer code as either regular memory references or irregular memory references. Moreover, the mechanisms may transform the computer code, by a compiler, to generate transformed computer code in which irregular memory references access a storage of a software cache of a data processing system through a transactional cache mechanism of the software cache.