The third generation of the Lagarto family of processors, designed entirely at BSC, represents a step forward in the development of high-performance European chips.

Based on RISC-V open hardware technology, the new processor is an important advance to achieve European technological sovereignty and reducing dependence on large multinational corporations

The BSC, Europe's leading developer of open source computing technologies, is committed to turning Barcelona into an innovation hub specialising in semiconductor design

The Barcelona Supercomputing Center - Centro Nacional de Supercomputación (BSC-CNS) presented on Wednesday the new Sargantana chip, the third generation of open source processors designed entirely at the BSC. The development of Sargantana is a crucial step forward in reinforcing BSC's leading position in RISC-V open source computing technology research in Europe.

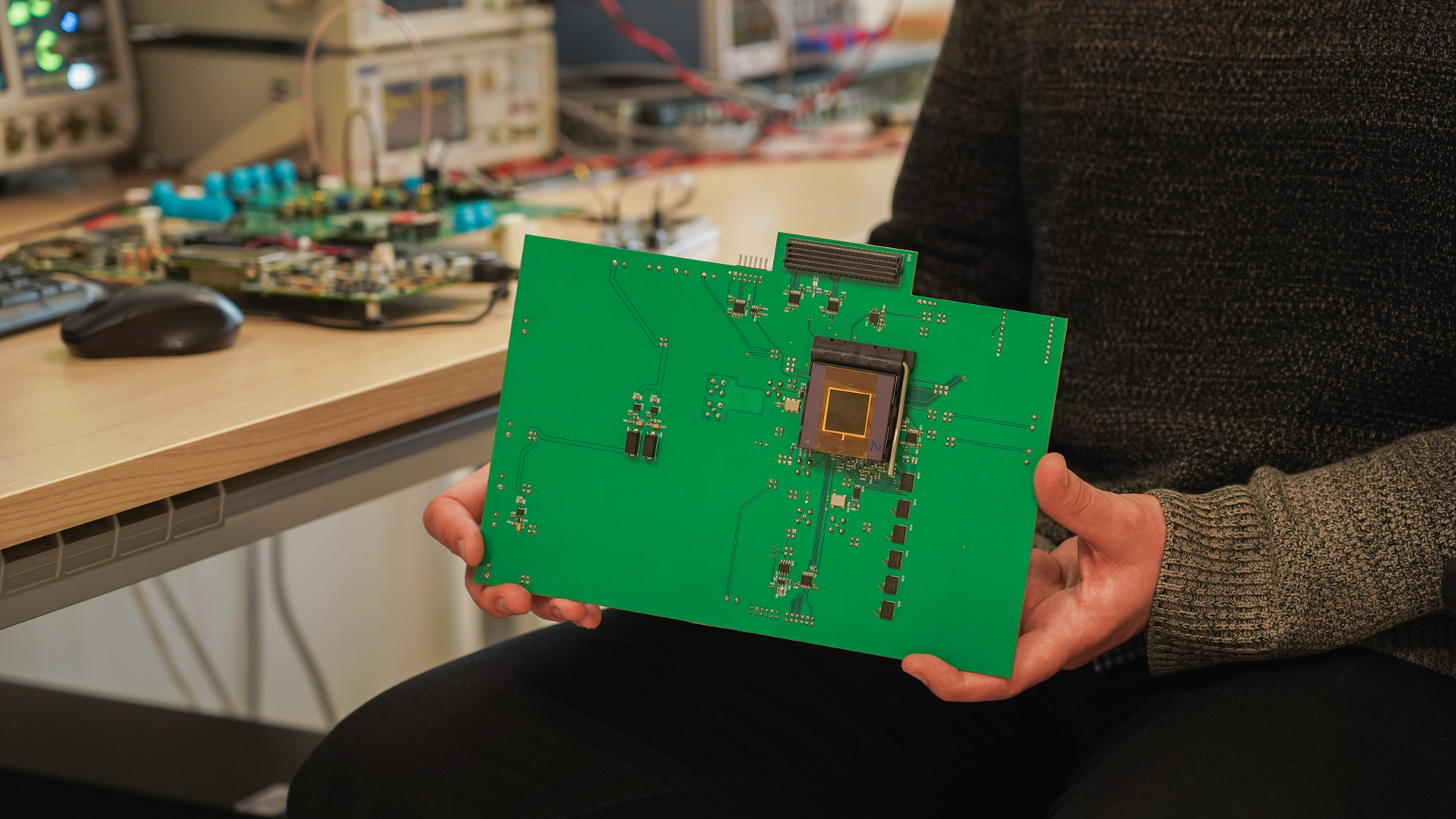

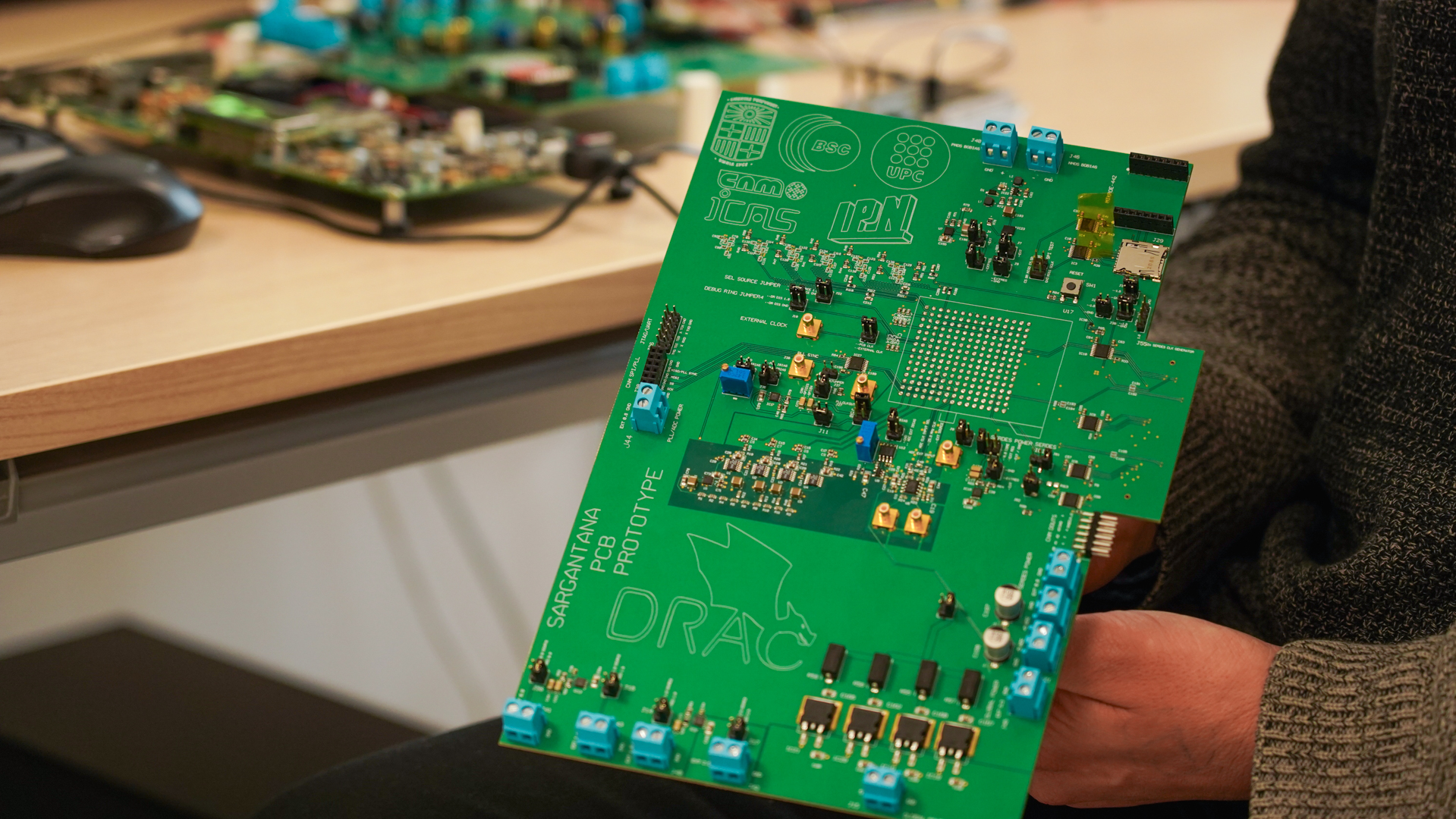

Sargantana (the name of the lizard in Aragonese and Catalan) is the third generation of the Lagarto processors, the first open source chips developed in Spain, in the framework of the DRAC project (Designing RISC-V-based Accelerators for next generation Computers), and is one of the most advanced open source chips in Europe at the academic level. The new Sargantana features better performance than its two predecessors - Lagarto Hun (2019) and DVINO (2021) - and is the first processor in the Lagarto family to break the gigahertz barrier in operating frequency.

The fact that the instruction set architecture (ISA) of these new processors is open source, and therefore non-proprietary and accessible to all, reduces technological dependence on large multinational corporations by enabling innovation through the collaboration of companies and institutions without the limitations of proprietary architectures. The RISC-V free hardware architecture, on which these new chips are based, could bring about a technological revolution in the hardware world like Linux did in the software world.

"The launch of Sargantana is a further step forward in the development of European RISC-V based technology, an embryo of the future European high-performance processor. This open hardware will be vital to ensure technological sovereignty and maintain European industrial competitiveness, and consolidates the BSC's role as a pioneer in Europe in the introduction of open source for chip design," said BSC director Mateo Valero.

In 2017, the European Union identified the lack of own hardware as one of the main vulnerabilities, due to the risk of industrial espionage posed by an over-reliance on chips designed and produced outside Europe, especially in the United States, Taiwan, China, Japan and South Korea. The BSC was then tasked by the EU to lead the scientific development of future European chips to provide the market with an open and local alternative, suitable for high-performance computing, artificial intelligence, the automotive sector and the internet of things.

Joint work coordinated by the BSC

Researchers from other universities and research centres such as the Centro de Investigación en Computación del Instituto Politécnico Nacional de México (CIC-IPN), the Institut de Microelectrònica de Barcelona - Centro Nacional de Microelectrónica (IMB-CNM, CSIC), the Universitat Politècnica de Catalunya (UPC), the Universitat Autònoma de Barcelona (UAB), the Universitat de Barcelona (UB) and the Universitat Rovira i Virgili (URV) have participated in the development of Sargantana.

The project was coordinated by BSC researcher Miquel Moretó, who highlighted the advantages of open-source semiconductor design to enable collaboration between companies and academic institutions around the world. "The new Sargantana chip is freely available to all, enabling a new era of processor innovation through open collaboration in which anyone, anywhere can benefit from RISC-V technology," he said.

Moretó pointed out that Sargantana is an experimental chip, a research prototype that will allow us to test applications with RISC-V technology and deepen our knowledge, but it is not yet designed to be used in computers or other devices. "We are developing a technology that will allow Spain and Europe to design their own increasingly competitive processors in the future, in addition to training future professionals in a sector that will undoubtedly add great value to the production chain," added Moretó, who highlighted the joint efforts of Catalonia, Spain and Europe to have European technology made in Barcelona and to train engineers in this field.

European leadership in RISC-V

This objective is in line with the idea pointed out by Mateo Valero of making Barcelona an international benchmark in processor design. "We have the talent, the technological knowledge and the scientific environment necessary for Barcelona and its surroundings to be able to compete with any institution or region in the world and become a Design Valley that drives the creation of companies and new jobs", said Valero.

The Sargantana presentation ceremony was held at the BSC facilities in Barcelona as part of the first day of the Spanish Open Hardware Alliance (SOHA), an association that brings together Spanish universities and research centres with the aim of promoting research in the area of Open Computer Technology and Architecture, thus contributing to the training of talent that allows the creation of high quality jobs.