Barcelona, 2-5 de Octubre de 2017.- Investigadores del BSC han publicado los primeros parámetros de tiempo fiables y detallados de la memoria Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), permitiendo una simulación fiable a nivel de sistema de esta tecnología. Los parámetros han sido hoy presentados en la conferencia titulada The International Symposium on Memory Systems 2017 (MEMSYS) que tiene lugar entre el 2 y el 5 de octubre de 2017 en la ciudad de Washington DC. El enfoque del BSC en la simulación de memoria STT-MRAM se ha realizado con la cooperación de Everspin Technologies Inc., líder mundial en el diseño y producción de STT-MRAM.

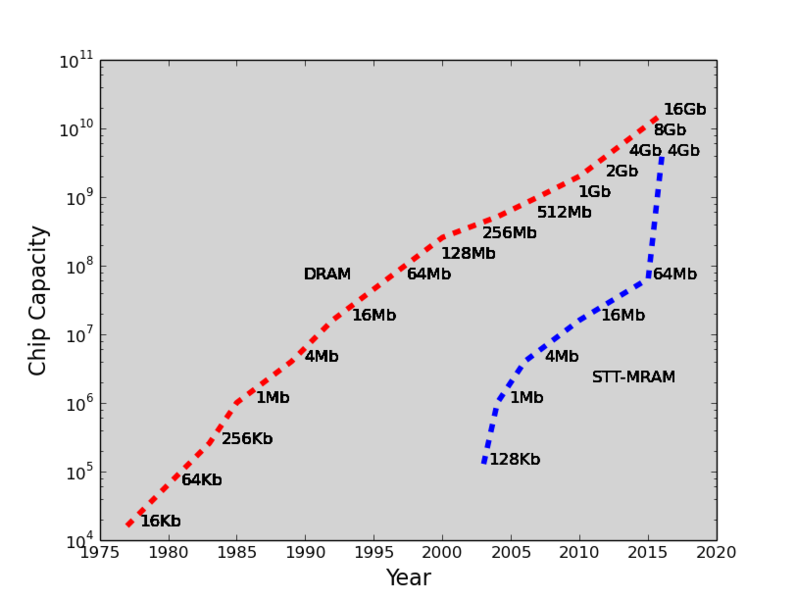

STT-MRAM es una tecnología de memoria prometedora con un conjunto de propiedades muy atractivas tales como la no-volatilidad, byte-addressability y una alta resistencia. Tiene el potencial de convertirse en la memoria universal que podría incorporarse en todos los niveles de la jerarquía de la memoria. Como memoria principal, STT-MRAM está alcanzando rápidamente a la tecnología DRAM madura, tal y como se muestra en la Figura 1; como resultado, ha atraído un notable interés por parte de un gran número de los principales fabricantes de memoria. Sin embargo, la investigación académica actual en STT-MRAM es marginal, debido principalmente a que no se han estandarizado ni compartido por ninguna industria parámetros de tiempo bien definidos y fiables. De ese modo, los investigadores siguen teniendo problemas para realizar una simulación de memoria STT-MRAM fiable.

“Un esfuerzo intensificado en la investigación de STT-MRAM por parte de los fabricantes de memoria puede ser indicativo de que una revolución con la tecnología de memoria STT-MRAM es inminente, y esperamos ver muchos logros interesantes en esta tecnología en un futuro próximo. Ahora que se han publicado parámetros de tiempo detallados y fiables, instamos encarecidamente a la academia que explore las oportunidades que esta tecnología tiene por ofrecer” concluye Petar Radojkovic, líder de Memory Systems for HPC en el BSC.

Con el objetivo de superar este problema, el estudio del BSC analiza a fondo y publica parámetros de tiempo detallados acerca de la memoria STT-MRAM para facilitar una simulación fiable a nivel de sistema de esta tecnología. El estudio se basa en el hecho que los dispositivos de memoria STT-MRAM están y serán incorporados en el protocolo e interface de DDRx, indicando que la mayoría de timings no cambiarán de la memoria DRAM a STT-MRAM. En cuanto a los parámetros que sí van a ser diferentes debido a las diferencias entre las célula de almacenaje DRAM y STT-MRAM, lo mejor que se puede hacer es un análisis de sensibilidad de éstos. El estudio también sugiere rangos razonables para estos timings que se verifican con productos comercializados.

Figura 2: Kazi Asifuzzaman (estudiante pre-doctoral en el BSC) presentando a la MEMSYS Conference 2017.