La tercera generación de procesadores de la familia Lagarto, diseñados íntegramente en el BSC, supone un paso adelante en el desarrollo de chips europeos de altas prestaciones.

Basado en la tecnología de hardware libre RISC-V, el nuevo procesador es un importante avance para conseguir la soberanía tecnológica europea y reducir la dependencia de las grandes corporaciones multinacionales

El BSC, líder en Europa en el desarrollo de tecnologías de computación de código abierto, apuesta por convertir Barcelona en un polo de innovación especializado en el diseño de semiconductores

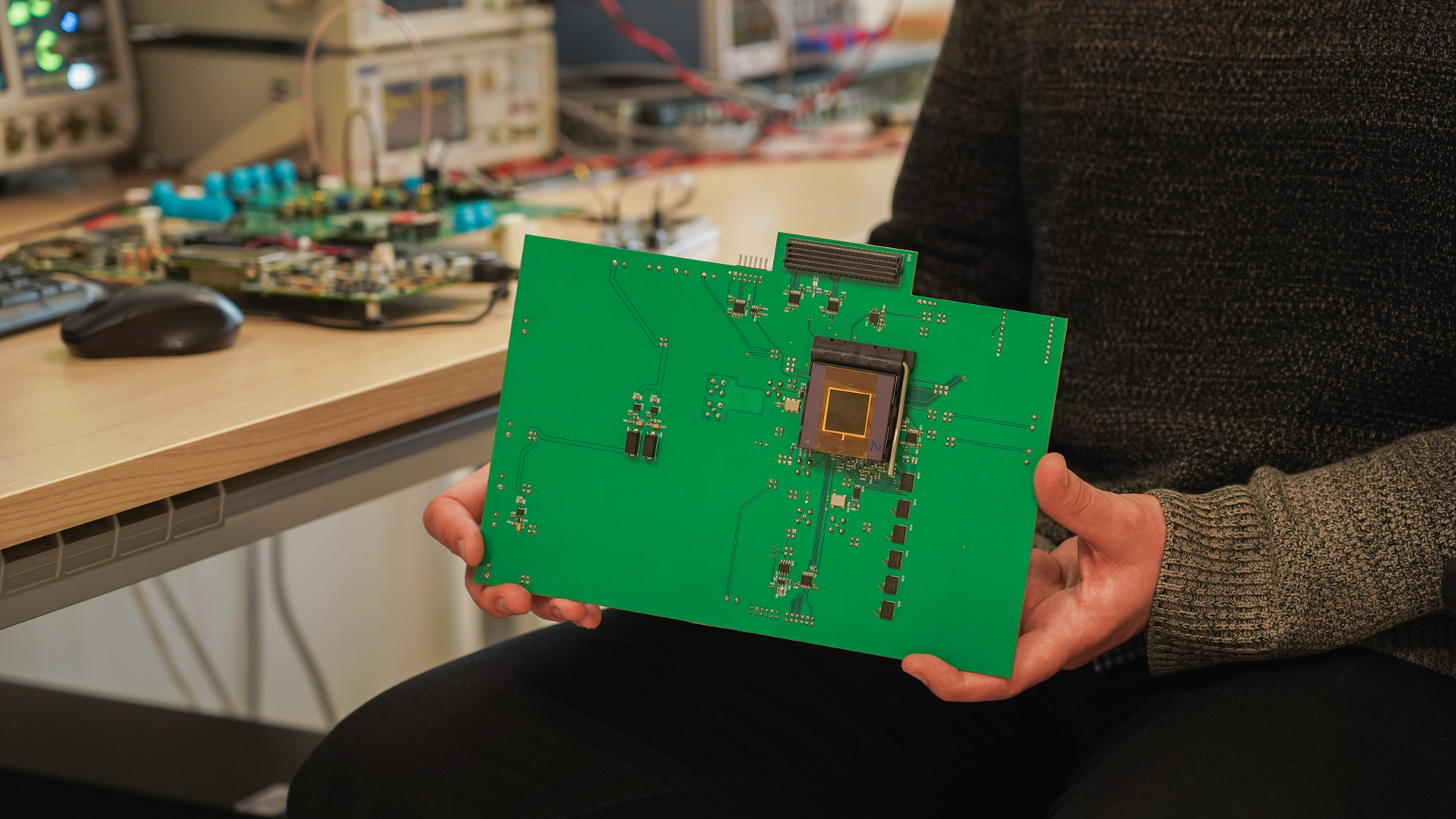

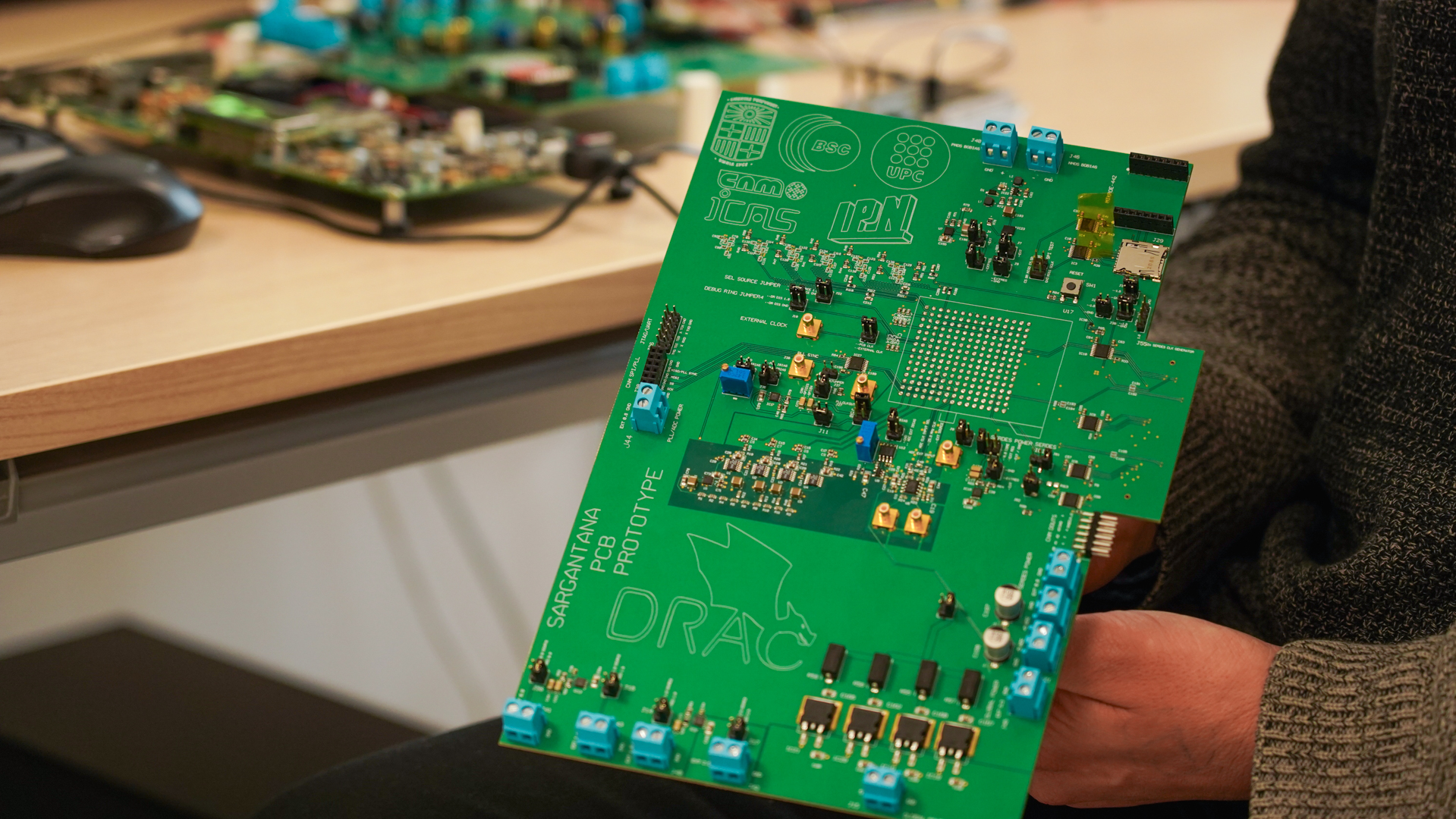

El Barcelona Supercomputing Center – Centro Nacional de Supercomputación (BSC-CNS) ha presentado este miércoles el nuevo chip Sargantana, la tercera generación de procesadores de código abierto diseñados íntegramente en el BSC. El desarrollo de Sargantana es un paso adelante crucial para reforzar la posición de liderazgo del BSC en la investigación en tecnologías de computación de código abierto RISC-V en Europa.

Sargantana (nombre de lagartija en aragonés y catalán) constituye la tercera generación de los procesadores Lagarto, los primeros chips de código abierto (open source) desarrollados en España, en el marco del proyecto DRAC (Designing RISC-V-based Accelerators for next generation Computers), y es uno de los chips de código abierto más avanzados de Europa a nivel académico. El nuevo Sargantana presenta una mejor prestación de rendimiento que sus dos predecesores -Lagarto Hun (2019) y DVINO (2021)- y es el primer procesador de la familia Lagarto que rompe la barrera del gigahercio en la frecuencia de trabajo.

El hecho de que el repertorio de instrucciones (ISA) de estos nuevos procesadores sea de código abierto, y por tanto sin propietario y accesible para todos, reduce la dependencia tecnológica de las grandes corporaciones multinacionales, al permitir la innovación a través de la colaboración de empresas e instituciones sin las limitaciones que implican las arquitecturas propietarias. La arquitectura de hardware libre RISC-V, en la que están basados estos nuevos chips, podría suponer una revolución tecnológica en el mundo del hardware como la que supuso Linux para el mundo del software.

“La presentación de Sargantana es un nuevo paso adelante en el desarrollo de tecnología europea basada en RISC-V, un embrión del futuro procesador europeo de altas prestaciones. Este hardware libre será vital para garantizar la soberanía tecnológica y mantener la competitividad industrial europea, y consolida el papel del BSC como pionero en Europa en la introducción del código abierto para el diseño de chips”, ha asegurado el director del BSC, Mateo Valero.

La Unión Europea identificó, en 2017, la carencia de hardware propio como una de las principales vulnerabilidades, por el riesgo de espionaje industrial que supone una dependencia excesiva de los chips diseñados y producidos fuera de Europa, especialmente en Estados Unidos, Taiwán, China, Japón y Corea del Sur. Entonces, el BSC recibió el encargo de la UE de liderar el desarrollo científico de los futuros chips europeos para dotar al mercado de una alternativa libre y local, apta para la computación de altas prestaciones, la inteligencia artificial, el sector del automóvil y el internet de las cosas.

Trabajo conjunto coordinado por el BSC

En el desarrollo de Sargantana han participado investigadores de otras universidades y centros de investigación como el Centro de Investigación en Computación del Instituto Politécnico Nacional de México (CIC-IPN), el Institut de Microelectrònica de Barcelona - Centro Nacional de Microelectrónica (IMB-CNM, CSIC), la Universitat Politècnica de Catalunya (UPC), la Universitat Autònoma de Barcelona (UAB), la Universitat de Barcelona (UB) y la Universitat Rovira i Virgili (URV).

El proyecto lo ha coordinado el investigador del BSC Miquel Moretó, quien ha subrayado las ventajas del diseño de semiconductores de código abierto para permitir la colaboración de empresas e instituciones académicas de todo el mundo. “El nuevo chip Sargantana está disponible para todos de forma gratuita, permitiendo una nueva era de innovación de procesadores a través de la colaboración abierta en la que cualquier persona de cualquier lugar podrá beneficiarse de la tecnología RISC-V”, ha afirmado.

Moretó ha precisado que Sargantana es un chip experimental, un prototipo de investigación que permitirá probar aplicaciones con tecnología RISC-V y profundizar en el conocimiento, pero todavía no está pensado para utilizarse en ordenadores ni en otros dispositivos. "Estamos desarrollando una tecnología que permitirá en un futuro a España y Europa diseñar sus propios procesadores cada vez más competitivos, además de formar a los futuros profesionales de un sector que sin duda aportará gran valor a la cadena productiva", ha añadido Moretó, que ha destacado el esfuerzo conjunto de Cataluña, España y Europa para tener tecnología europea hecha en Barcelona y formar ingenieros en este campo.

Liderazgo europeo en RISC-V

Este objetivo se alinea con la idea señalada por Mateo Valero de convertir a Barcelona en un polo de referencia internacional en el diseño de procesadores. "Tenemos el talento, el conocimiento tecnológico y el entorno científico necesarios para que Barcelona y su entorno pueda competir con cualquier institución o región del mundo y convertirse en un Design Valley que impulse la creación de empresas y nuevos puestos de trabajo", ha indicado Valero.

El acto de presentación de Sargantana se ha celebrado en las instalaciones del BSC en Barcelona en el marco de la primera jornada de la Spanish Open Hardware Alliance (SOHA), asociación que agrupa a universidades y centros de investigación españoles con el objetivo de impulsar la investigación en el área de Tecnología y Arquitectura de Computadores en abierto, contribuyendo así a la formación de talento que permita la creación de puestos de trabajo de alta calidad.