Published on BSC-CNS (https://www.bsc.es)

Inicio > Dependable and power-efficient real-time systems

## Dependable and power-efficient real-time systems

We propose several methodologies, techniques, and tools to help with the development of reliable and power-efficient real-time systems. Our designs are done in compliance with the safety-critical standards applicable in the corresponding domain (e.g. ISO26262 for automotive).

## Summary

The need for increased functionality has forced designers of safety-relevant embedded systems to include more computation and memory resources within a single chip. The integration of a higher number of transistors in the same chip cannot be achieved without using smaller technology nodes that suffer increased process variability. Small imperfections in transistors and wires introduced in the manufacturing process become more significant as they are a significant fraction of the feature size. Additionally, as the number of transistors per unit area increases, extra care is required to keep power density below a certain threshold.

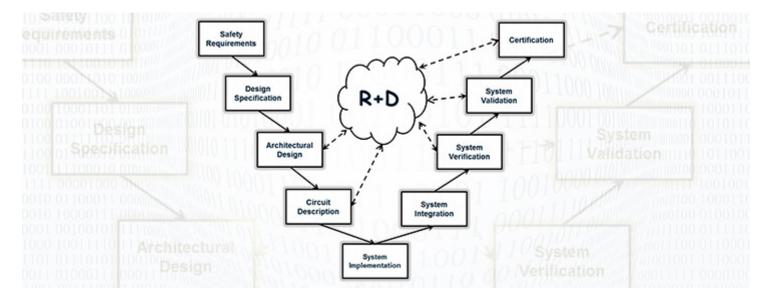

The design of reliable and power-efficient complex modern electronic designs for safety-critical markets requires also adhering to the strict requirements of functional safety standards. Thus, those designs have to undergo an expensive and time-consuming certification process, which is against the always stringent need to reduce the time to market. We focus our research on facilitating the development of dependable and power-efficient real-time systems that comply with the safety-critical standards.

## **Objectives**

In this research front we pursue the following objectives:

- 1. Designing reliable and power-efficient real-time systems adhering to safety-critical standards

- 2. Developing quick and cost-effective methodologies to test whether reliability and power requirements are satisfied throughout the whole design flow

Barcelona Supercomputing Center - Centro Nacional de Supercomputación

**Source URL** (**retrieved on 7** *Mayo* **2024 - 01:57**): <a href="https://www.bsc.es/es/research-development/research-areas/computer-architecture-and-codesign/dependable-and-power">https://www.bsc.es/es/research-development/research-areas/computer-architecture-and-codesign/dependable-and-power</a>